機械学習における訓練処理を高速化する計算方式と回路を考案したと、産業技術総合研究所が発表しました。高速化が困難な訓練の処理能力を最大で5倍に向上できることが確認されました。

機械学習では訓練処理によって生成されるモデルのできが推論の正確性を左右するため、大量のデータで訓練処理を行う必要があります。

また、訓練処理は推論処理と比べて高い数値計算の精度が要求されるため、非常に大きな処理能力が必要となり、処理のための時間や消費電力が課題となっています。

機械学習の訓練処理では通常、32ビットまたは64ビットの数値表現が使われます。ビット数を大きくすると計算制度が向上する一方で、処理のための回路は大きくなり、処理時間や消費電力が増大してしまいます。

逆にビット数を小さくすると、処理時間や消費電力は減少するものの、計算精度が悪化することになります。

そこで研究グループは、限られたビット数ですべてのデータを精度よく表現できるデータ形式と、ビット数が小さくても訓練処理における乗算や加算を正確に実行できる計算方式を考案しました。

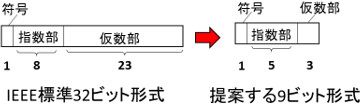

今回考案された「9ビットデータ形式」は、符合1ビット、指数部5ビット、仮数部3ビットで構成されます。

32ビット形式の場合は演算回路のおよそ8割を乗算回路が占めますが、9ビット形式では仮数部が3ビットに減ったため乗算回路が32ビット形式と比べて30分の1程度となります。

また、指数部が8ビットから5ビットに減り、演算回路への入力が32ビットから9ビットに減ったことでデータをメモリーなどから演算回路へ移動するエネルギーも4分の1まで削減されます。

一方で、生成モデルによる推論の精度への影響が大きい加算回路については、仮数部を23ビットとして学習精度を保っています。

これによって数値計算の精度劣化を引き起こす情報落ちを防ぎ、訓練処理の精度が向上します。加算回路では仮数部を23ビットと増やしても、回路全体の大きさへの影響は大きくありません。

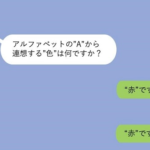

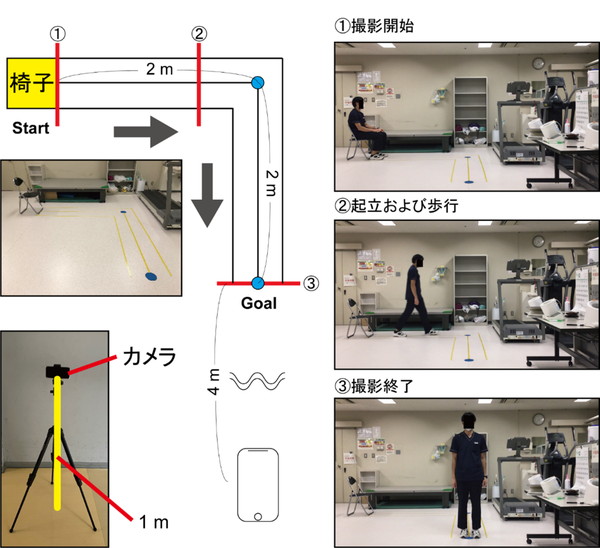

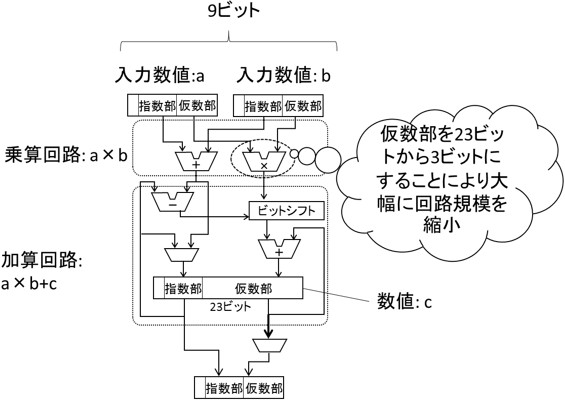

図は今回考案された計算方式を実行するための回路を示しています。

機械学習の訓練処理では、2つの数値(a、b)を乗算して内部に保存された数値cに加算する「積和演算」が多く使われます。

今回考案された回路では、2つの入力値を9ビット形式で受けて乗算してから乗算結果の仮数部を23ビットに変換。ビットシフト処理で桁合わせをした後で23ビットで加算を行います。加算結果は再び9ビット形式に変換してから出力します。

この計算方式と回路を用いた推論の精度と消費電力について、シミュレーションで推定したところ、32ビット形式と比べて精度劣化は2%程度まで抑えられ、回路規模と必要な消費電力は5分の1程度に抑制できることが確認されました。

このことは、同じ規模のハードウェアを使った場合に処理能力が5倍程度に高速化できることを示しています。

今回考案された回路を実装したプロセッサを活用すれば、機械学習によるモデル生成にかかる時間が大幅に短縮され、新たなビジネスチャンスや利用者の利便性向上につながることが期待されます。